The first or second paragraph should’ve said “ASML generates 250W EUV finally ending up 5W EUV due to reflection, whereas this will end up with 1kW EUV for chip production”. It wasn’t clear at all why they were doing this until 3/4 through the article. And I assume it’s 1kW EUV as the source and with less mirrors possibly 20W or more on the wafer (?).

Maybe I missed it, but it doesn’t mention the amount of energy required to end up with this 20W EUV beam. A particle accelerator probably uses more, but maybe the productivity balances out the efficiency?

I don’t think it mentions the amount of energy required either, it mentions that there is less noise with the particle accelerator approach which looks to be the main advantage.

I figure the increased power getting to the etching process also helps increase throughput. I’m guessing that you only need a total amount of energy to do a unit of etching work, so with more power you can do more units of etching work per unit time.

That sounds plausible, and you could also likely sustain energy output easier with this setup which will help with the throughput as well. It seems like a big design constraint on ASML machines is that they wanted them to be portable so they could ship them to customers in different countries. Once you remove that constraint you get some benefits at the cost of the sheer size of the facility.

Unfortunately it was paywalled.

I’m not an expert, but ASML uses a very powerful ultraviolet ‘cannon’ to edge patterns into their layers https://wikiless.northboot.xyz/wiki/Extreme_ultraviolet_lithography, and apparently (from the few lines of article txt) the Chinese are going for particle accelerators for edging instead. I wonder if they will use a beam or just fire away on a masked wafer.

Slightly ot, I think hybrid photonic computing is the future, but that would probably also benefit from smaller construction techniques, so …go go China.

If someone is interested in chip construction and new AI trends in that area, I can recommend ‘Asianometry’ https://www.youtube.com/channel/UC1LpsuAUaKoMzzJSEt5WImw / https://redirect.invidious.io/channel/UC1LpsuAUaKoMzzJSEt5WImw and especially ‘Anastacia in tech’ https://www.youtube.com/channel/UCORX3Cl7ByidjEgzSCgv9Yw / https://redirect.invidious.io/channel/UCORX3Cl7ByidjEgzSCgv9Yw

They have not reported on this Chinese particle thing yet, tho…

here’s an archived version https://archive.ph/NrC6B

it does mention the advantages over ASML approach

Compared with current ASML EUV technology, SSMB is a more ideal light source. It has a higher average power and higher chip production output with lower unit cost.

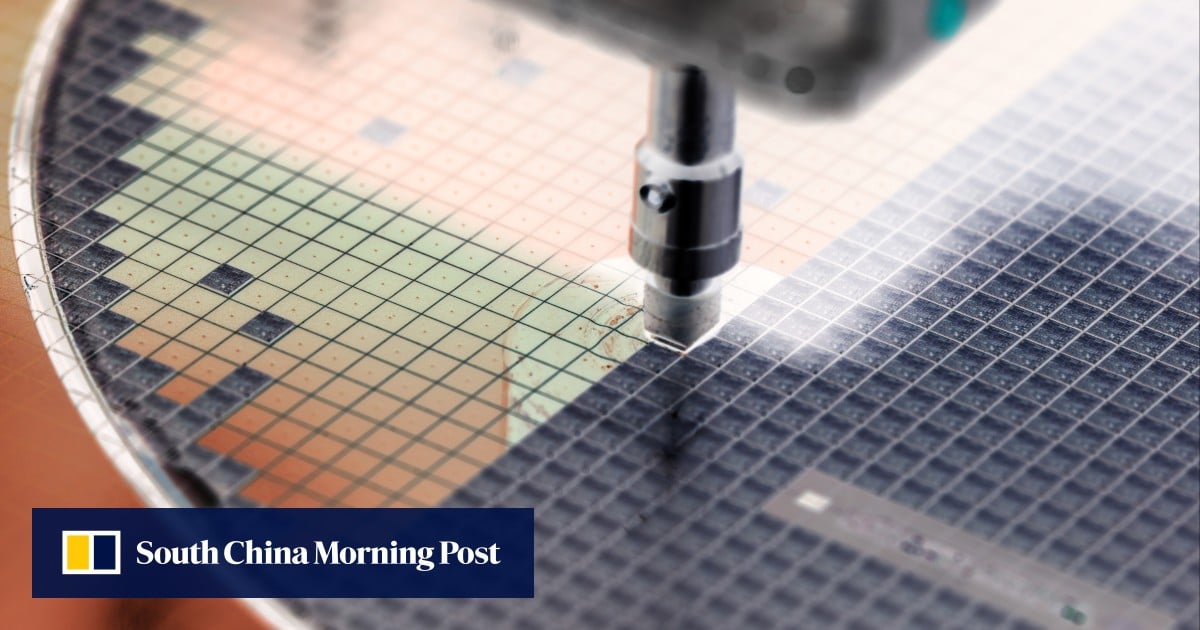

ASML creates an EUV source from laser-produced plasma, where strong laser pulses are projected to liquid microdroplets of tin. The laser crushes the droplets and produces EUV pulse light during the impact. After complex filtering and focusing, an EUV light source with a power of about 250W is produced.

Before reaching the chip, the EUV beam undergoes reflection from 11 mirrors, each causing about a 30 per cent energy loss. As a result, the power of the beam is less than 5W when reaching the wafer. This can become an issue when manufacturing turns to 3nm or 2nm.

SSMB technology avoids such concerns. SSMB beams achieve a higher output power of 1000W, and due to its narrow bandwidth, fewer reflecting mirrors are needed, which naturally generates higher terminal power.

I do think there is a lot of potential for alternative computing substrates like photonics or graphene.

Incidentally, there was a breakthrough fabricating 12-inch wafers with MoS2 which has potential to be a much faster substrate than silicon https://www.sciencedirect.com/science/article/abs/pii/S2095927323004206

This kind of stuff could end up being like going from vacuum tubes to transistors. We’re pushing the limits of what’s physically possible with silicon now, but even a crude alternative substrate could naturally afford far better performance, and then could be optimized for decades on end.

Damn, things are moving fast atmo ! Thx for info!

Here is an alternative Piped link(s):

https://www.piped.video/channel/UC1LpsuAUaKoMzzJSEt5WImw

https://www.piped.video/channel/UCORX3Cl7ByidjEgzSCgv9Yw

Piped is a privacy-respecting open-source alternative frontend to YouTube.

I’m open-source; check me out at GitHub.

How is this an improvement over traditional construction. Seems like a giant waste of energy and money.

Seems like you didn’t bother reading the article which explains the advantages very clearly. People passing judgment on things they have no clue about will never stop being hilarious.

I’m glad you found my comment hilarious. I found the title hilarious, fortunately the article has a better one.